Diferencia entre revisiones de «Relevamiento Grupo 2»

(→Sero: links) |

m |

||

| (No se muestran 14 ediciones intermedias de 3 usuarios) | |||

| Línea 1: | Línea 1: | ||

| + | [[Category:Descontinuadas]] | ||

| + | |||

| + | |||

| + | Dentro del mundo de los procesadores, los más utilizados son los '''RISC''' y dentro de esta familia tenemos '''ARM''' y '''MIPS'''. Estos son usados típicamente en dispositivos como routers, tarjetas de video, "smartphones", etc. | ||

| + | |||

| + | Las características fundamentales de estos procesadores son: | ||

| + | |||

| + | * Bajo costo | ||

| + | * Propósito General | ||

| + | * Instrucciones simples y de corto tiempo de ejecución | ||

| + | |||

| + | Hoy en día, el procesador más usado es el '''ARM''' con el 75% de los procesadores del mercado. | ||

| + | |||

| + | A continuación dejamos una reseña de algunos de estos procesadores que se encuentran hoy en el mercado. | ||

| + | |||

== NVIDIA Tegra 2: == | == NVIDIA Tegra 2: == | ||

| Línea 16: | Línea 31: | ||

'''Referencia:''' http://arg.nvidia.com/object/tegra-2-la.html | '''Referencia:''' http://arg.nvidia.com/object/tegra-2-la.html | ||

| + | Este procesador es utilizado tanto en "smartphones" como en las tarjetas gráficas NVIDIA. | ||

== Apple A4: == | == Apple A4: == | ||

| Línea 21: | Línea 37: | ||

El '''Apple A4''' es un System on chip, que integra un microprocesador basado en la arquitectura ARM; y una GPU PowerVR 535 en un mismo encapsulado. | El '''Apple A4''' es un System on chip, que integra un microprocesador basado en la arquitectura ARM; y una GPU PowerVR 535 en un mismo encapsulado. | ||

| − | Procesador: | + | '''Procesador:''' |

CPU ARM v7: Cortex A8 | CPU ARM v7: Cortex A8 | ||

Frequency 1 GHz | Frequency 1 GHz | ||

| Línea 57: | Línea 73: | ||

'''Referencias:''' http://es.wikipedia.org/wiki/Intel_Atom | '''Referencias:''' http://es.wikipedia.org/wiki/Intel_Atom | ||

| − | == | + | == RISC == |

| + | En la arquitectura computacional, RISC (del inglés reduced instruction set computer) es un tipo de microprocesador con las siguientes características fundamentales: | ||

| − | === Sero === | + | Instrucciones de tamaño fijo y presentadas en un reducido número de formatos. |

| + | Sólo las instrucciones de carga y almacenamiento acceden a la memoria de datos. | ||

| + | |||

| + | Además estos procesadores suelen disponer de muchos registros de propósito general. | ||

| + | |||

| + | El objetivo de diseñar máquinas con esta arquitectura es posibilitar la segmentación y el paralelismo en la ejecución de instrucciones y reducir los accesos a memoria. Las máquinas RISC protagonizan la tendencia actual de construcción de microprocesadores. PowerPC, DEC Alpha, MIPS, ARM, ... son ejemplos de algunos de ellos. | ||

| + | |||

| + | RISC es una filosofía de diseño de CPU para computadora que está a favor de conjuntos de instrucciones pequeñas y simples que toman menor tiempo para ejecutarse. El tipo de procesador más comúnmente utilizado en equipos de escritorio, el x86, está basado en CISC en lugar de RISC, aunque las versiones más nuevas traducen instrucciones basadas en CISC x86 a instrucciones más simples basadas en RISC para uso interno antes de su ejecución. | ||

| + | |||

| + | La idea fue inspirada por el hecho de que muchas de las características que eran incluidas en los diseños tradicionales de CPU para aumentar la velocidad estaban siendo ignoradas por los programas que eran ejecutados en ellas. Además, la velocidad del procesador en relación con la memoria de la computadora que accedía era cada vez más alta. Esto conllevó la aparición de numerosas técnicas para reducir el procesamiento dentro del CPU, así como de reducir el número total de accesos a memoria. | ||

| + | |||

| + | Terminología más moderna se refiere a esos diseños como arquitecturas de carga-almacenamiento. | ||

| + | |||

| + | === Procesadores ARM === | ||

| + | |||

| + | ==== Sero ==== | ||

{| class="wikitable" border="1" style="width:100%;" | {| class="wikitable" border="1" style="width:100%;" | ||

| Línea 76: | Línea 108: | ||

|Nulo | |Nulo | ||

| | | | ||

| − | |ARM Evaluation System segundo procesador para | + | |ARM Evaluation System segundo procesador para BBC Micro |

|- | |- | ||

! rowspan=2 | ARM2 | ! rowspan=2 | ARM2 | ||

| Línea 232: | Línea 264: | ||

|16 KB/16 KB, MMU con FCSE (Fast Context Switch Extension)[http://infocenter.arm.com/help/topic/com.arm.doc.ddi0151c/I47491.html Register 13, FCSE PID register] ARM920T Technical Reference Manual | |16 KB/16 KB, MMU con FCSE (Fast Context Switch Extension)[http://infocenter.arm.com/help/topic/com.arm.doc.ddi0151c/I47491.html Register 13, FCSE PID register] ARM920T Technical Reference Manual | ||

|200 MIPS @ 180 MHz | |200 MIPS @ 180 MHz | ||

| − | |Armadillo, Atmel AT91SAM9, GP32, GP2X (primer núcleo), Tapwave Zodiac (Motorola i. MX1), Hewlett-Packard Calculadoras HP-49/50 , Sun SPOT, Cirrus Logic EP9302, EP9307, EP9312, EP9315, Samsung S3C2442 (HTC TyTN, FIC Neo | + | |Armadillo, Atmel AT91SAM9, GP32, GP2X (primer núcleo), Tapwave Zodiac (Motorola i. MX1), Hewlett-Packard Calculadoras HP-49/50 , Sun SPOT, Cirrus Logic EP9302, EP9307, EP9312, EP9315, Samsung S3C2442 (HTC TyTN, FIC Neo [http://wiki.openmoko.org/wiki/Neo1973:_GTA01Bv4_versus_GTA02_comparison Neo1973: GTA01Bv4 versus GTA02 comparison]), Samsung S3C2410 (Dispositivos de navegación TomTom) [http://elinux.org/S3C2410 S3C2410] |

|- | |- | ||

|ARM922T | |ARM922T | ||

| Línea 244: | Línea 276: | ||

|4 KB/4 KB, MPU | |4 KB/4 KB, MPU | ||

| | | | ||

| − | |GP2X (segundo núcleo), Meizu M6 Mini Player | + | |GP2X (segundo núcleo), Meizu M6 Mini Player [http://www.rockbox.org/twiki/bin/view/Main/SamsungSA58 Rockbox Samsung SA58xxx series] [http://www.rockbox.org/twiki/bin/view/Main/MeizuM6Port Rockbox Meizu M6 Port – Hardware Information] |

|- | |- | ||

! rowspan=5 | ARM9E | ! rowspan=5 | ARM9E | ||

| Línea 258: | Línea 290: | ||

|sin caché, TCMs | |sin caché, TCMs | ||

| | | | ||

| − | |ST Micro STR91xF, integra Ethernet | + | |ST Micro STR91xF, integra Ethernet [http://mcu.st.com/mcu/modules.php?name=mcu&file=devicedocs&DEV=STR912FW44&FAM=101 STR9 – STR912 – STR912FW44 microcontroller – documents and files download page |editorial=Mcu.st.com] |

|- | |- | ||

|ARM968E-S | |ARM968E-S | ||

| Línea 313: | Línea 345: | ||

| | | | ||

|400/600 MHz | |400/600 MHz | ||

| − | | | + | |Thecus N2100 |

|- | |- | ||

|IOP321 | |IOP321 | ||

| Línea 342: | Línea 374: | ||

| | | | ||

|32KB/32KB, MMU | |32KB/32KB, MMU | ||

| − | |400 BogoMips @ 400 MHz; 371–533 MIPS @ 400 MHz | + | |400 BogoMips @ 400 MHz; 371–533 MIPS @ 400 MHz [http://www.albatross-uav.org/index.php/Benchmarks Benchmarks – Albatross] |

|Gumstix basix & connex, Palm Tungsten E2, Zaurus SL-C860, Mentor Ranger & Stryder, iRex ILiad | |Gumstix basix & connex, Palm Tungsten E2, Zaurus SL-C860, Mentor Ranger & Stryder, iRex ILiad | ||

|- | |- | ||

| Línea 409: | Línea 441: | ||

| | | | ||

| | | | ||

| − | | | + | |NSLU2 IXP460/IXP465 |

|- | |- | ||

!rowspan=4 | ARM11 | !rowspan=4 | ARM11 | ||

|ARMv6 | |ARMv6 | ||

| − | |ARM1136J(F)-S | + | |ARM1136J(F)-S [http://www.arm.com/products/CPUs/ARM1136JF-S.html ARM1136J(F)-S – ARM Processor] |

|Segmentación de 8 etapas, SIMD, Thumb, Jazelle DBX, (VFP), Mejora de instrucciones DSP | |Segmentación de 8 etapas, SIMD, Thumb, Jazelle DBX, (VFP), Mejora de instrucciones DSP | ||

|variable, MMU | |variable, MMU | ||

|740 @ 532–665 MHz (i.MX31 SoC), 400–528 MHz | |740 @ 532–665 MHz (i.MX31 SoC), 400–528 MHz | ||

| − | |Texas Instruments OMAP2420 (Nokia E90, Nokia N93, Nokia N95, Nokia N82), Zune, BUGbase[http://www.buglabs.net/], Nokia N800, Nokia N810, Qualcomm MSM7200 (con coprocesador ARM926EJ-S@274 MHz, usado en Eten Glofiish, HTC TyTN II, HTC Nike), Freescale i.MX31 (del Zune original de 30 GB, Toshiba Gigabeat S y Kindle DX), Freescale MXC300-30 (Nokia E63, Nokia E71, Nokia 5800, Nokia E51, Nokia 6700 Classic, Nokia 6120 Classic, Nokia 6210 Navigator, Nokia 6220 Classic, Nokia 6290, Nokia 6710 Navigator, Nokia 6720 Classic, Nokia E75, Nokia N97, Nokia N81), Qualcomm MSM7201A visto en los HTC Dream, HTC Magic, Motorola Z6, HTC Hero, & Samsung SGH-i627 (Propel Pro), Qualcomm MSM7227 usado en ZTE Link, | + | |Texas Instruments OMAP2420 (Nokia E90, Nokia N93, Nokia N95, Nokia N82), Zune, BUGbase[http://www.buglabs.net/], Nokia N800, Nokia N810, Qualcomm MSM7200 (con coprocesador ARM926EJ-S@274 MHz, usado en Eten Glofiish, HTC TyTN II, HTC Nike), Freescale i.MX31 (del Zune original de 30 GB, Toshiba Gigabeat S y Kindle DX), Freescale MXC300-30 (Nokia E63, Nokia E71, Nokia 5800, Nokia E51, Nokia 6700 Classic, Nokia 6120 Classic, Nokia 6210 Navigator, Nokia 6220 Classic, Nokia 6290, Nokia 6710 Navigator, Nokia 6720 Classic, Nokia E75, Nokia N97, Nokia N81), Qualcomm MSM7201A visto en los HTC Dream, HTC Magic, Motorola Z6, HTC Hero, & Samsung SGH-i627 (Propel Pro), Qualcomm MSM7227 usado en ZTE Link,[http://xi0.info/qualcomm-chips-kernel-arm-phones_7000.html Qualcomm chips kernel ARM - from phones to laptops][http://pdadb.net/index.php?m=cpu&id=a7227&c=qualcomm_msm7227 Qualcomm MSM7227 RISC Chipset] |

|- | |- | ||

|ARMv6T2 | |ARMv6T2 | ||

| Línea 431: | Línea 463: | ||

|variable, MMU+TrustZone | |variable, MMU+TrustZone | ||

| | | | ||

| − | |Apple iPhone (EDGE y 3G), Apple iPod touch (1ra y 2da generación), Conexant CX2427X, Motorola RIZR Z8, Motorola RIZR Z10, NVIDIA GoForce 6100; | + | |Apple iPhone (EDGE y 3G), Apple iPod touch (1ra y 2da generación), Conexant CX2427X, Motorola RIZR Z8, Motorola RIZR Z10, NVIDIA GoForce 6100;[http://www.nvidia.com/page/goforce_6100.html GoForce 6100] Telechips TCC9101, TCC9201, TCC8900, Fujitsu MB86H60, Samsung S3C6410 (ej. Samsung Omnia II, Samsung Moment, SmartQ 5), S3C6430[http://www.samsung.com/global/business/semiconductor/productInfo.do?fmly_id=229&partnum=S3C6410 Samsung S3C6410 and S3C6430 Series ARM Proccessors], y el Qualcomm MSM7627 visto en el Palm Pixi y el Motorola Calgary/Devour |

|- | |- | ||

|ARMv6K | |ARMv6K | ||

| Línea 438: | Línea 470: | ||

|variable, MMU | |variable, MMU | ||

| | | | ||

| − | |[[Nvidia APX 2500 | + | |[[Nvidia APX 2500 |

|- | |- | ||

! Familia | ! Familia | ||

| Línea 454: | Línea 486: | ||

|variable (L1), MMU+TrustZone | |variable (L1), MMU+TrustZone | ||

|Más de 1500 (1.5 DMIPS/MHz) | |Más de 1500 (1.5 DMIPS/MHz) | ||

| − | |"Sparrow" (nombre en clave) | + | |"Sparrow" (nombre en clave)[http://www.eetimes.com/showArticle.jhtml?articleID=220700447 ARM stretches out with A5 core, graphics, FPGAs [http://www.eetimes.com/news/semi/rss/showArticle.jhtml?articleID=213000665&cid=RSSfeed_eetimes_semiRSS ARM tips plans for Swift and Sparrow processor cores] [http://www.pcmag.com/article2/0,2817,2341032,00.asp ARM's Multicore Chips Aim for Netbooks] |

|- | |- | ||

|Cortex-A8 | |Cortex-A8 | ||

| Línea 487: | Línea 519: | ||

|- | |- | ||

|ARMv7-ME | |ARMv7-ME | ||

| − | |Cortex-M4 (nombre en clave "Merlin") | + | |Cortex-M4 (nombre en clave "Merlin")[http://www.heise.de/newsticker/meldung/Cortex-Nachwuchs-bei-ARM-936412.html Cortex Nachwuchs bei ARM] |

|Perfil microcontrolador, Thumb y Thumb-2, FPU. MAC, SIMD e instrucciones divididas. | |Perfil microcontrolador, Thumb y Thumb-2, FPU. MAC, SIMD e instrucciones divididas. | ||

|MPU opcional. | |MPU opcional. | ||

| Línea 501: | Línea 533: | ||

|- | |- | ||

|rowspan=2 |ARMv6-M | |rowspan=2 |ARMv6-M | ||

| − | |Cortex-M0 (nombre en clave "Swift") | + | |Cortex-M0 (nombre en clave "Swift")[http://www.eetimes.com/news/design/rss/showArticle.jhtml?articleID=214502333 ARM preps tiny core for low-power microcontrollers] |

|Perfil microcontrolador, Thumb-2 subset (instrucciones 16-bit Thumb & BL, MRS, MSR, ISB, DSB, and DMB). | |Perfil microcontrolador, Thumb-2 subset (instrucciones 16-bit Thumb & BL, MRS, MSR, ISB, DSB, and DMB). | ||

|Sin caché. | |Sin caché. | ||

|0.9 DMIPS/MHz | |0.9 DMIPS/MHz | ||

| − | |NXP Semiconductors [http://www.standardics.nxp.com/products/lpc1000/lpc11xx/ NXP LPC1100], | + | |NXP Semiconductors [http://www.standardics.nxp.com/products/lpc1000/lpc11xx/ NXP LPC1100],[http://www.eetimes.com/news/design/rss/showArticle.jhtml?articleID=216200026 NXP first to demo ARM Cortex-M0 silicon] Triad Semiconductor,http://www.triadsemi.com/services/arm-powered-vcas/ Melfas,[http://www.electronicsweekly.com/Articles/2009/06/10/46252/cortex-m0-used-in-low-power-touch-controller.htm Cortex-M0 used in low power touch controller] Chungbuk Technopark,http://www.design-reuse.com/news/22137/arm-cortex-m0-processor.html Nuvoton,http://translate.google.co.uk/translate?hl=en&sl=zh-TW&u=http://www.nuvoton.com/hq/enu/NewsAndEvents/News/MediaCoverage/20091005.htm austriamicrosystems,http://www10.edacafe.com/nbc/articles/view_article.php?articleid=752000 Rohm http://www.arm.com/about/newsroom/rohm-licenses-arm-cortex-m0-processor.php |

|- | |- | ||

| | | | ||

| Línea 524: | Línea 556: | ||

|} | |} | ||

| − | Referencias: http://es.wikipedia.org/wiki/ARM | + | '''Referencias:''' |

| + | http://es.wikipedia.org/wiki/ARM | ||

| + | |||

| + | === Procesadores MIPS === | ||

| + | |||

| + | Con el nombre de MIPS (siglas de Microprocessor without Interlocked Pipeline Stages) se conoce a toda una familia de microprocesadores de arquitectura RISC desarrollados por MIPS Technologies. | ||

| + | |||

| + | Los diseños del MIPS son utilizados en la línea de productos informáticos de SGI; en muchos sistemas embebidos; en dispositivos para Windows CE; routers Cisco; y videoconsolas como la Nintendo 64 o las Sony PlayStation, PlayStation 2 y PlayStation Portable. | ||

| + | |||

| + | Las primeras arquitecturas MIPS fueron implementadas en 32 bits (generalmente rutas de datos y registros de 32 bits de ancho), si bien versiones posteriores fueron implementadas en 64 bits. Existen cinco revisiones compatibles hacia atrás del conjunto de instrucciones del MIPS, llamadas MIPS I, MIPS II, MIPS III, MIPS IV y MIPS 32/64. En la última de ellas, la MIPS 32/64 Release 2, se define a mayores un conjunto de control de registros. Así mismo están disponibles varias "extensiones", tales como la MIPS-3D consistente en un simple conjunto de instrucciones SIMD en coma flotante dedicadas a tareas 3D comunes, la MDMX(MaDMaX) compuesta por un conjunto más extenso de instrucciones SIMD enteras que utilizan los registros de coma flotante de 64 bits, la MIPS16 que añade compresión al flujo de instrucciones para hacer que los programas ocupen menos espacio (presuntamente como respuesta a la tecnología de compresión Thumb de la arquitectura ARM) o la reciente MIPS MT que añade funcionalidades multithreading similares a la tecnología HyperThreading de los procesadores Intel Pentium 4. | ||

| + | |||

| + | Debido a que los diseñadores crearon un conjunto de instrucciones tan claro, los cursos sobre arquitectura de computadores en universidades y escuelas técnicas a menudo se basan en la arquitectura MIPS. El diseño de la familia de CPU's MIPS influiría de manera importante en otras arquitecturas RISC posteriores como los DEC Alpha. | ||

| + | |||

| + | El uso del MIPS como procesador principal de estaciones de trabajo ha caído, y SGI ha anunciado sus planes de cesar el desarrollo de iteraciones de alto rendimiento de la arquitectura MIPS en favor de procesadores basados en la tecnología Intel IA64 (véase la sección "Otros modelos y planes futuros"). | ||

| + | |||

| + | Por otra parte, el uso de microprocesadores MIPS en sistemas embebidos es probable que se mantenga gracias al bajo consumo de energía y características térmicas de las implementaciones integradas, así como a la gran disponibilidad de herramientas de desarrollo y de expertos conocedores de la arquitectura. | ||

| + | |||

| + | En los últimos años gran parte de la tecnología empleada en las distintas generaciones MIPS ha sido ofrecida como diseños de "IP-cores" (bloques de construcción) para sistemas embebidos. Se ofertan los núcleos básicos de 32 y 64 bits, conocidos respectivamente como 4K y 5K respectivamente, y con licencias MIPS32 y MIPS64. Estos núcleos pueden ser combinados con unidades añadidas tales como FPUs, sistemas SIMD, dispositivos de E/S, etc. | ||

| + | |||

| + | Los núcleos MIPS han sido comercialmente exitosos, siendo empleados actualmente en muchas aplicaciones industriales y de consumo. Pueden encontrarse en los más modernos routers Cisco y Linksys , cablemódems y módems ADSL, tarjetas inteligentes, controladoras de impresoras láser, decodificadores de TV, robots, ordenadores de mano, Sony PlayStation 2 y Sony PlayStation Portable. | ||

| + | |||

| + | En móviles y PDA's, sin embargo, el núcleo MIPS fue incapaz de desbancar a su competidor de arquitectura ARM. | ||

| + | |||

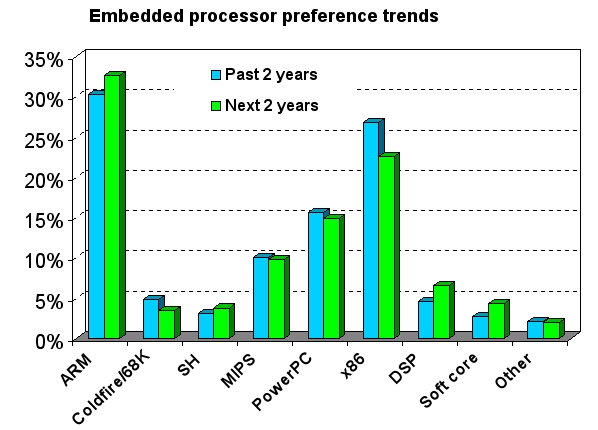

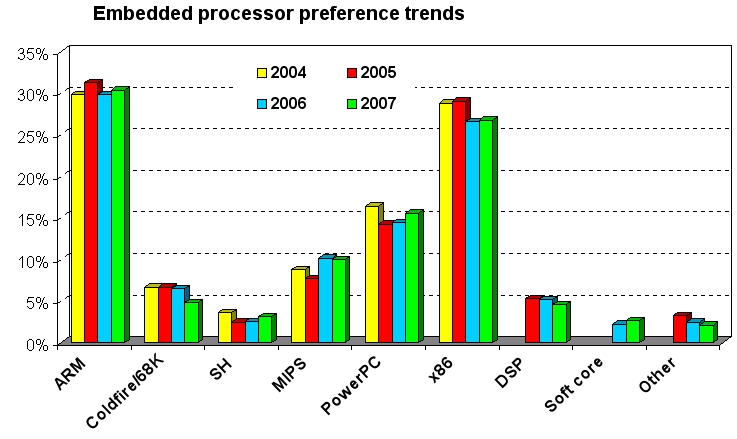

| + | == Tendencia de preferencia de procesadores embebidos == | ||

| + | |||

| + | [[Archivo:embedded_processor_current_trend.jpg]] | ||

| + | |||

| + | [[Archivo:embedded_processor_preference_history.jpg]] | ||

| + | |||

| + | Encuesta realizada en el año 2007 por el sitio [http://www.linuxfordevices.com Linux for devices] | ||

| + | |||

| + | == Referencias: == | ||

| + | http://es.wikipedia.org/wiki/ARM | ||

| + | |||

| + | http://es.wikipedia.org/wiki/MIPS_%28procesador%29 | ||

| + | |||

| + | http://mips.com/products/cores/ | ||

| + | |||

| + | http://es.wikipedia.org/wiki/RISC | ||

| + | |||

| + | http://www.linuxfordevices.com/c/a/Linux-For-Devices-Articles/Snapshot-of-the-embedded-Linux-market-April-2007/ | ||

Revisión actual - 17:15 14 ene 2022

Dentro del mundo de los procesadores, los más utilizados son los RISC y dentro de esta familia tenemos ARM y MIPS. Estos son usados típicamente en dispositivos como routers, tarjetas de video, "smartphones", etc.

Las características fundamentales de estos procesadores son:

- Bajo costo

- Propósito General

- Instrucciones simples y de corto tiempo de ejecución

Hoy en día, el procesador más usado es el ARM con el 75% de los procesadores del mercado.

A continuación dejamos una reseña de algunos de estos procesadores que se encuentran hoy en el mercado.

NVIDIA Tegra 2:

NVIDIA® Tegra™ 2 es el procesador móvil más avanzado del mundo. Cuenta con la primera CPU de doble núcleo móvil del mundo para ofrecer una navegación en la Web con hasta el doble de la velocidad.

CPU de doble núcleo ARM Cortex-A9 GPU GeForce con ULP ("ultra low power" o consumo ultra reducido de energía)

Especificaciones:

Procesador: CPU Dual-Core ARM Cortex A9 Frequency 1 GHz, per core L2 Cache 1 MB L1 Cache (I/D) (32KB / 32KB) per core

Referencia: http://arg.nvidia.com/object/tegra-2-la.html

Este procesador es utilizado tanto en "smartphones" como en las tarjetas gráficas NVIDIA.

Apple A4:

El Apple A4 es un System on chip, que integra un microprocesador basado en la arquitectura ARM; y una GPU PowerVR 535 en un mismo encapsulado.

Procesador: CPU ARM v7: Cortex A8 Frequency 1 GHz

Referencia: http://es.wikipedia.org/wiki/Apple_A4

Snapdragon

Snapdragon es una plataforma ARM desarrollada por Qualcomm para dispositivos móviles. Su diseño responde a las necesidades de uso de ordenador en tiempo real, en cualquier lugar, y con una duración de batería equivalente a una jornada.

El más reciente chip QSD8672,usa tecnología de 45 nm e incluye dos núcleos corriendo hasta un máximo de 1.5GHz. QSD8672 va a ser empleado en dispositivos smartphone e incluye HSPA+ integrado, GPS, Bluetooth, grabación y reproducción de video de alta definición, Wi-Fi y tecnologías de TV móvil (MediaFLO, DVB-H y ISDB-T).1

El primer MID que va a usar Snapdragon a 1GHz es el smartphone TG01.2

Qualcomm asegura que su arquitectura será capaz de gestionar pantallas de hasta 12" con una resolución de hasta 1440x900 pixels (WSXGA).3

Referencias: http://es.wikipedia.org/wiki/Snapdragon_%28procesador%29

Intel Atom

Intel® Atom™ es el nombre de una línea de microprocesadores x86 y x86-64 de Intel, anteriormente denominados Silverthorne/Diamondville. Están diseñados para un proceso de fabricación de 45 nm CMOS y destinados a utilizarse en dispositivos móviles de Internet (MID, por sus siglas en inglés), Ultra-portátiles, Teléfonos inteligentes, y otros portátiles de baja potencia y aplicaciones.

Procesador:

CPU Intel® Atom™

Frequency 800 MHz a 2,0 GHz

Velocidad de

FSB 533 y 667 MT/s

Procesos 0,045 µm

Conjuto de

instrucciones x86, x86-64

Zócalo(s) 441-ball µFCBGA (Micro-FCBGA)

Núcleo(s) Silverthorne/Diamondville

Referencias: http://es.wikipedia.org/wiki/Intel_Atom

RISC

En la arquitectura computacional, RISC (del inglés reduced instruction set computer) es un tipo de microprocesador con las siguientes características fundamentales:

Instrucciones de tamaño fijo y presentadas en un reducido número de formatos. Sólo las instrucciones de carga y almacenamiento acceden a la memoria de datos.

Además estos procesadores suelen disponer de muchos registros de propósito general.

El objetivo de diseñar máquinas con esta arquitectura es posibilitar la segmentación y el paralelismo en la ejecución de instrucciones y reducir los accesos a memoria. Las máquinas RISC protagonizan la tendencia actual de construcción de microprocesadores. PowerPC, DEC Alpha, MIPS, ARM, ... son ejemplos de algunos de ellos.

RISC es una filosofía de diseño de CPU para computadora que está a favor de conjuntos de instrucciones pequeñas y simples que toman menor tiempo para ejecutarse. El tipo de procesador más comúnmente utilizado en equipos de escritorio, el x86, está basado en CISC en lugar de RISC, aunque las versiones más nuevas traducen instrucciones basadas en CISC x86 a instrucciones más simples basadas en RISC para uso interno antes de su ejecución.

La idea fue inspirada por el hecho de que muchas de las características que eran incluidas en los diseños tradicionales de CPU para aumentar la velocidad estaban siendo ignoradas por los programas que eran ejecutados en ellas. Además, la velocidad del procesador en relación con la memoria de la computadora que accedía era cada vez más alta. Esto conllevó la aparición de numerosas técnicas para reducir el procesamiento dentro del CPU, así como de reducir el número total de accesos a memoria.

Terminología más moderna se refiere a esos diseños como arquitecturas de carga-almacenamiento.

Procesadores ARM

Sero

| Familia | Versión de Arquitectura | Núcleo | Características | Cache (I/D)/MMU | Millones de instrucciones por segundo(MIPS) efectivos @ MHz | Campos de Aplicación |

|---|---|---|---|---|---|---|

| ARM1 | ARMv1 (obsoleto) | ARM1 | Nulo | ARM Evaluation System segundo procesador para BBC Micro | ||

| ARM2 | ARMv2 (obsoleto) | ARM2 | Añadida instrucción MUL (multiplicar) | Nulo | 4 MIPS @ 8 MHz 0.33 DMIPS/MHz |

Acorn Archimedes, Chessmachine |

| ARMv2a (obsoleto) | ARM250 | Integrado MEMC (MMU), gráficos y un procesador de E / S. Añadidas instrucciones SWP y SWPB (swap). | Nulo, MEMC1a | 7 MIPS @ 12 MHz | Acorn Archimedes | |

| ARM3 | ARMv2a (obsoleto) | ARM2a | Primera integración de una memoria caché en un ARM. | 4K unificados | 12 MIPS @ 25 MHz 0.50 DMIPS/MHz |

Acorn Archimedes |

| ARM6 | ARMv3 (obsoleto) | ARM60 | Soporte de dirección de memoria de 32 bits (frente a los 26 bits) | Nulo | 10 MIPS @ 12 MHz | 3DO Interactive Multiplayer, Zarlink GPS Receiver |

| ARM600 | Como ARM60, caché y un bus cooprocesador (para la unidad de coma flotante FPA10). | 4K unificados | 28 MIPS @ 33 MHz | |||

| ARM610 | Como ARM60, caché, sin bus coprocesador. | 4K unificados | 17 MIPS @ 20 MHz 0.65 DMIPS/MHz |

Acorn Risc PC 600, Apple Newton Serie 100 | ||

| ARM7 | ARMv3 (obsoleto) | ARM700 | 8 KB unificados | 40 MHz | Acorn Risc PC prototipo de CPU card | |

| ARM710 | Como ARM700 | 8 KB unificados | 40 MHz | Acorn Risc PC 700 | ||

| ARM710a | Como ARM700 | 8 KB unificados | 40 MHz 0.68 DMIPS/MHz |

Acorn Risc PC 700, Apple eMate 300 | ||

| ARM7100 | Como ARM710a, SoC integrado. | 8 KB unificados | 18 MHz | Psion Series 5 | ||

| ARM7500 | Como ARM710a, SoC integrado. | 4 KB unificados | 40 MHz | Acorn A7000 | ||

| ARM7500FE | ARM7500, "FE" añadido un FPA y un controlador de memoria EDO. | 4 KB unificados | 56 MHz 0.73 DMIPS/MHz |

Acorn A7000+ Network Computer | ||

| ARM7TDMI | ARMv4T | ARM7TDMI(-S) | Segmentación de 3 etapas, Thumb | nulo | 15 MIPS @ 16.8 MHz 63 DMIPS @ 70 MHz |

Game Boy Advance, Nintendo DS, Apple iPod, Lego NXT, Atmel AT91SAM7, Juice Box, NXP Semiconductors LPC2000 and LH754xx, Actel's CoreMP7 |

| ARM710T | ARM7TDMI, caché | 8 KB unificados, MMU | 36 MIPS @ 40 MHz | Psion Series 5mx, Psion Revo/Revo Plus/Diamond Mako | ||

| ARM720T | ARM7TDMI, caché | 8 KB unificados, MMU con FCSE | 60 MIPS @ 59.8 MHz | Zipit Wireless Messenger, NXP Semiconductors LH7952x | ||

| ARM740T | ARM7TDMI, caché | MPU | ||||

| ARMv5TEJ | ARM7EJ-S | Segmentación de 5 etapas, Thumb, Jazelle DBX, mejora de instruciones DSP | nulo | |||

| StrongARM | ARMv4 | SA-110 | 16 KB/16 KB, MMU | 203 MHz 1.0 DMIPS/MHz |

Apple Newton serie 2x00 , Acorn Risc PC, Rebel/Corel Netwinder, Chalice CATS | |

| SA-1100 | SA-110, SoC integrado | 16 KB/8 KB, MMU | 203 MHz | Psion netBook | ||

| SA-1110 | SA-110, SoC integrado | 16 KB/8 KB, MMU | 206 MHz | LART (computer), Intel Assabet, Ipaq H36x0, Balloon2, Zaurus SL-5x00, HP Jornada 7xx, Jornada 560 series, Palm Zire 31 | ||

| ARM8 | ARMv4 | ARM810"ARM810 – Dancing to the Beat of a Different Drum" ARM Holdings presentation at Hot Chips 1996-08-07. | Segmentación de 5 fases, predilección de salto estático, memoria de doble ancho de banda | 8 KB unificados, MMU | 84 MIPS @ 72 MHz 1.16 DMIPS/MHz |

Acorn Risc PC prototipo de CPU card |

| ARM9TDMI | ARMv4T | ARM9TDMI | Segmentación de 5 fases, Thumb | nulo | ||

| ARM920T | ARM9TDMI, caché | 16 KB/16 KB, MMU con FCSE (Fast Context Switch Extension)Register 13, FCSE PID register ARM920T Technical Reference Manual | 200 MIPS @ 180 MHz | Armadillo, Atmel AT91SAM9, GP32, GP2X (primer núcleo), Tapwave Zodiac (Motorola i. MX1), Hewlett-Packard Calculadoras HP-49/50 , Sun SPOT, Cirrus Logic EP9302, EP9307, EP9312, EP9315, Samsung S3C2442 (HTC TyTN, FIC Neo Neo1973: GTA01Bv4 versus GTA02 comparison), Samsung S3C2410 (Dispositivos de navegación TomTom) S3C2410 | ||

| ARM922T | ARM9TDMI, cachés | 8 KB/8 KB, MMU | NXP Semiconductors LH7A40x | |||

| ARM940T | ARM9TDMI, cachés | 4 KB/4 KB, MPU | GP2X (segundo núcleo), Meizu M6 Mini Player Rockbox Samsung SA58xxx series Rockbox Meizu M6 Port – Hardware Information | |||

| ARM9E | ARMv5TE | ARM946E-S | Thumb, mejora de instrucciones DSP, caché | variables, memoria estrechamente acoplada, MPU | Nintendo DS, Nokia N-Gage, Canon PowerShot A470, Canon EOS 5D Mark II,[1] Conexant 802.11 chips, Samsung S5L2010 | |

| ARM966E-S | Thumb, Mejora de instrucciones DSP | sin caché, TCMs | editorial=Mcu.st.com] | |||

| ARM968E-S | ARM966E-S | sin caché, TCMs | NXP Semiconductors LPC2900 | |||

| ARMv5TEJ | ARM926EJ-S | Thumb, Jazelle DBX, Mejora de instrucciones DSP | variables, TCMs, MMU | 220 MIPS @ 200 MHz, | Teléfonos móviles: Sony Ericsson (K, W series); Siemens y Benq (serie x65 y posterior); LG Arena; Texas Instruments OMAP1710, OMAP1610, OMAP1611, OMAP1612, OMAP-L137, OMAP-L138; Qualcomm MSM6100, MSM6125, MSM6225, MSM6245, MSM6250, MSM6255A, MSM6260, MSM6275, MSM6280, MSM6300, MSM6500, MSM6800; Freescale i.MX21, i.MX27, Atmel AT91SAM9, NXP Semiconductors LPC3000, GPH Wiz, NEC C10046F5-211-PN2-A SoC – núcleo en la ATi Hollywood GPU usada en la Wii,Starlet. Samsung S3C2412 usado en Squeezebox Duet's Controller. Squeezebox Radio; NeoMagic MiMagic Family MM6, MM6+, MM8, MTV; Buffalo TeraStation Live (NAS); Telechips TCC7801, TCC7901;ZiiLABS' ZMS-05 SoC; Western Digital MyBook "I World Edition"; Rockchip RK2806 y RK2808. | |

| ARMv5TE | ARM996HS | Procesador sin reloj, como ARM966E-S | sin cachés, TCMs, MPU | |||

| ARM10E | ARMv5TE | ARM1020E | Segmentación de 6 fases, Thumb, Mejora de instrucciones DSP, (VFP) | 32 KB/32 KB, MMU | ||

| ARM1022E | ARM1020E | 16 KB/16 KB, MMU | ||||

| ARMv5TEJ | ARM1026EJ-S | Thumb, Jazelle DBX, Mejora de instrucciones DSP, (VFP) | variable, MMU o MPU | Western Digital MyBook "II World Edition";Conexant so4610 y so4615 ADSL SoC | ||

| XScale | ARMv5TE | 80200/IOP310/IOP315 | Procesador E/S, Thumb, Mejora de instrucciones DSP | |||

| 80219 | 400/600 MHz | Thecus N2100 | ||||

| IOP321 | 600 BogoMips @ 600 MHz | Iyonix | ||||

| IOP33x | ||||||

| IOP34x | 1–2 núcleos, Acelerador de RAID | 32K/32K L1, 512K L2, MMU | ||||

| PXA210/PXA250 | Procesador de aplicaciones, Segmentación de 7 fases | PXA210: 133 y 200 MHz, PXA250: 200, 300, and 400 MHz | Zaurus SL-5600, iPAQ H3900, Sony CLIÉ NX60, NX70V, NZ90 | |||

| PXA255 | 32KB/32KB, MMU | 400 BogoMips @ 400 MHz; 371–533 MIPS @ 400 MHz Benchmarks – Albatross | Gumstix basix & connex, Palm Tungsten E2, Zaurus SL-C860, Mentor Ranger & Stryder, iRex ILiad | |||

| PXA263 | 200, 300 y 400 MHz | Sony CLIÉ NX73V, NX80V | ||||

| PXA26x | default 400 MHz, más de 624 MHz | Palm Tungsten T3 | ||||

| PXA27x | Procesador de Aplicaciones | 32 KB/32 KB, MMU | 800 MIPS @ 624 MHz | Gumstix verdex,"Trizeps-Modules" PXA270 COM, HTC Universal, HP hx4700, Zaurus SL-C1000, 3000, 3100, 3200, Dell Axim x30, x50, and x51 series, Motorola Q, Balloon3, Trolltech Greenphone, Palm TX(312MHz), Motorola Ezx Platform A728, A780, A910, A1200, E680, E680i, E680g, E690, E895, Rokr E2, Rokr E6, Fujitsu Siemens LOOX N560, Toshiba Portégé G500, Trēo 650-755p, Zipit Z2, HP iPaq 614c Business Navigator. | ||

| PXA800(E)F | ||||||

| PXA3XX (nombre en clave "Monahans") | 32KB/32KB L1, TCM, MMU | 1000 MIPS @ 1.25 GHz | Samsung Omnia | |||

| PXA900 | Blackberry 8700, Blackberry Pearl (8100) | |||||

| IXC1100 | Procesador de control de vuelo | |||||

| IXP2400/IXP2800 | ||||||

| IXP2850 | ||||||

| IXP2325/IXP2350 | ||||||

| IXP42x | NSLU2 IXP460/IXP465 | |||||

| ARM11 | ARMv6 | ARM1136J(F)-S ARM1136J(F)-S – ARM Processor | Segmentación de 8 etapas, SIMD, Thumb, Jazelle DBX, (VFP), Mejora de instrucciones DSP | variable, MMU | 740 @ 532–665 MHz (i.MX31 SoC), 400–528 MHz | Texas Instruments OMAP2420 (Nokia E90, Nokia N93, Nokia N95, Nokia N82), Zune, BUGbase[2], Nokia N800, Nokia N810, Qualcomm MSM7200 (con coprocesador ARM926EJ-S@274 MHz, usado en Eten Glofiish, HTC TyTN II, HTC Nike), Freescale i.MX31 (del Zune original de 30 GB, Toshiba Gigabeat S y Kindle DX), Freescale MXC300-30 (Nokia E63, Nokia E71, Nokia 5800, Nokia E51, Nokia 6700 Classic, Nokia 6120 Classic, Nokia 6210 Navigator, Nokia 6220 Classic, Nokia 6290, Nokia 6710 Navigator, Nokia 6720 Classic, Nokia E75, Nokia N97, Nokia N81), Qualcomm MSM7201A visto en los HTC Dream, HTC Magic, Motorola Z6, HTC Hero, & Samsung SGH-i627 (Propel Pro), Qualcomm MSM7227 usado en ZTE Link,Qualcomm chips kernel ARM - from phones to laptopsQualcomm MSM7227 RISC Chipset |

| ARMv6T2 | ARM1156T2(F)-S | Segmentación de 9 etapas, SIMD, Thumb-2, (VFP), Mejora de instrucciones DSP | variable, MPU | |||

| ARMv6KZ | ARM1176JZ(F)-S | ARM1136EJ(F)-S | variable, MMU+TrustZone | Apple iPhone (EDGE y 3G), Apple iPod touch (1ra y 2da generación), Conexant CX2427X, Motorola RIZR Z8, Motorola RIZR Z10, NVIDIA GoForce 6100;GoForce 6100 Telechips TCC9101, TCC9201, TCC8900, Fujitsu MB86H60, Samsung S3C6410 (ej. Samsung Omnia II, Samsung Moment, SmartQ 5), S3C6430Samsung S3C6410 and S3C6430 Series ARM Proccessors, y el Qualcomm MSM7627 visto en el Palm Pixi y el Motorola Calgary/Devour | ||

| ARMv6K | ARM11 MPCore | As ARM1136EJ(F)-S, 1–4 core SMP | variable, MMU | [[Nvidia APX 2500 | ||

| Familia | Versión de arquitectura | Núcleo | Características | Caché (I/D)/MMU | MIPS efectivos @ MHz | Campo de aplicación |

| Cortex | ARMv7-A | Cortex-A5 | VFP, NEON, Jazelle RCT and DBX, Thumb-2, Segmentación de 8 fases, 1–4 núcleos SMP | variable (L1), MMU+TrustZone | Más de 1500 (1.5 DMIPS/MHz) | "Sparrow" (nombre en clave)ARM stretches out with A5 core, graphics, FPGAs [http://www.eetimes.com/news/semi/rss/showArticle.jhtml?articleID=213000665&cid=RSSfeed_eetimes_semiRSS ARM tips plans for Swift and Sparrow processor cores ARM's Multicore Chips Aim for Netbooks |

| Cortex-A8 | VFP, NEON, Jazelle RCT, Thumb-2, Segmentación Superscalar de 13 etapas | variable (L1+L2), MMU+TrustZone | Más de 2000 (2.0 DMIPS/MHz de reloj desde 600 MHz hasta más de 1 GHz) | Texas Instruments serie OMAP3xxx, SBM7000, Oregon State University OSWALD, Gumstix Overo Earth, Pandora, Apple iPhone 3GS, Apple iPod touch (3rd Generation), Apple iPad (SoCApple A4), Apple iPhone 4 (Soc Apple A4 , fabricado por Samsung e Intrensity), Archos 5, FreeScale i.MX51-SOC, BeagleBoard, Motorola Milestone, Motorola Milestone X, Palm Pre, Samsung Omnia HD, Samsung Wave S8500 (Hummingbird), Samsung i9000 Galaxy S (Hummingbird), Sony Ericsson Satio, Touch Book, Nokia N900, Meizu M9, ZiiLABS ZMS-08 SoC. | ||

| Qualcomm Scorpion | GPU Adreno 200, VFPv3, NEON, Jazelle RCT, Thumb-2, Segmentación Superscalar de 13 etapas, | variable (L1+L2), MMU+TrustZone | Más de 2000 (2.0 DMIPS/MHz de reloj desde 1 GHz hasta más de 1,5 GHz dual core) | Toshiba TG01, HTC Desire, Google Nexus One, HTC EVO 4G, HTC Incredible, HTC Scorpion, HTC HD2, HTC HD7 | ||

| Cortex-A9 | Perfil de aplicaciones, (VFP), (NEON), Jazelle RCT y DBX, Thumb-2, Out-of-order speculative issue superscalar | MMU+TrustZone | 2.5 DMIPS/MHz | |||

| Cortex-A9 MPCore | Cortex-A9, 1–4 núcleos SMP | MMU+TrustZone | 10,000 DMIPS @ 2 GHz optimizados en TSMC 40G (Doble núcleo) (2.5 DMIPS/MHz por núcleo) | Texas Instruments OMAP4430/4440, ST-Ericsson U8500, Nvidia Tegra2, Qualcomm Snapdragon 8X72 PlayStation Vita | ||

| ARMv7-R | Cortex-R4(F) | Perfil Embebido, Thumb-2, (FPU) | variable caché, MPU opcional | 600 DMIPS @ 475 MHz | Broadcom, TMS570 from Texas Instruments | |

| ARMv7-ME | Cortex-M4 (nombre en clave "Merlin")Cortex Nachwuchs bei ARM | Perfil microcontrolador, Thumb y Thumb-2, FPU. MAC, SIMD e instrucciones divididas. | MPU opcional. | 1.25 DMIPS/MHz | ||

| ARMv7-M | Cortex-M3 | Perfil microcontrolador, Thumb-2 únicamente. Reparto de instrucciones por Hardware. | sin caché, MPU opcional. | 125 DMIPS @ 100 MHz | Texas Instruments Stellaris microcontroller family, ST Microelectronics STM32, NXP Semiconductors LPC1700, Toshiba TMPM330FDFG, Ember's EM3xx Series, Atmel AT91SAM3, Europe Technologies EasyBCU, Energy Micro's EFM32, Actel's SmartFusion | |

| ARMv6-M | Cortex-M0 (nombre en clave "Swift")ARM preps tiny core for low-power microcontrollers | Perfil microcontrolador, Thumb-2 subset (instrucciones 16-bit Thumb & BL, MRS, MSR, ISB, DSB, and DMB). | Sin caché. | 0.9 DMIPS/MHz | NXP Semiconductors NXP LPC1100,NXP first to demo ARM Cortex-M0 silicon Triad Semiconductor,http://www.triadsemi.com/services/arm-powered-vcas/ Melfas,Cortex-M0 used in low power touch controller Chungbuk Technopark,http://www.design-reuse.com/news/22137/arm-cortex-m0-processor.html Nuvoton,http://translate.google.co.uk/translate?hl=en&sl=zh-TW&u=http://www.nuvoton.com/hq/enu/NewsAndEvents/News/MediaCoverage/20091005.htm austriamicrosystems,http://www10.edacafe.com/nbc/articles/view_article.php?articleid=752000 Rohm http://www.arm.com/about/newsroom/rohm-licenses-arm-cortex-m0-processor.php | |

| Cortex-M1 | FPGA targeted, Microcontroller profile, Thumb-2 subset (instrucciones 16-bit Thumb & BL, MRS, MSR, ISB, DSB, and DMB). | Sin | Más de 136 DMIPS @ 170 MHz"ARM Extends Cortex Family with First Processor Optimized for FPGA", ARM press release, March 19, 2007. Retrieved April 11, 2007. (0.8 DMIPS/MHz,"ARM Cortex-M1", ARM product website. Retrieved April 11, 2007. MHz achievable FPGA-dependent) | Actel ProASIC3, ProASIC3L, IGLOO and Fusion PSC devices, Altera Cyclone III, otros productos FPGA están soportados, por ejemplo: Synplicity

ARM Extends Cortex Family with First Processor Optimized for FPGA. | ||

| Familia | Versión de Arquitectura | Núcleo | Características | Caché (I/D)/MMU | MIPS efectivos @ MHz | Campo de Aplicación |

Referencias: http://es.wikipedia.org/wiki/ARM

Procesadores MIPS

Con el nombre de MIPS (siglas de Microprocessor without Interlocked Pipeline Stages) se conoce a toda una familia de microprocesadores de arquitectura RISC desarrollados por MIPS Technologies.

Los diseños del MIPS son utilizados en la línea de productos informáticos de SGI; en muchos sistemas embebidos; en dispositivos para Windows CE; routers Cisco; y videoconsolas como la Nintendo 64 o las Sony PlayStation, PlayStation 2 y PlayStation Portable.

Las primeras arquitecturas MIPS fueron implementadas en 32 bits (generalmente rutas de datos y registros de 32 bits de ancho), si bien versiones posteriores fueron implementadas en 64 bits. Existen cinco revisiones compatibles hacia atrás del conjunto de instrucciones del MIPS, llamadas MIPS I, MIPS II, MIPS III, MIPS IV y MIPS 32/64. En la última de ellas, la MIPS 32/64 Release 2, se define a mayores un conjunto de control de registros. Así mismo están disponibles varias "extensiones", tales como la MIPS-3D consistente en un simple conjunto de instrucciones SIMD en coma flotante dedicadas a tareas 3D comunes, la MDMX(MaDMaX) compuesta por un conjunto más extenso de instrucciones SIMD enteras que utilizan los registros de coma flotante de 64 bits, la MIPS16 que añade compresión al flujo de instrucciones para hacer que los programas ocupen menos espacio (presuntamente como respuesta a la tecnología de compresión Thumb de la arquitectura ARM) o la reciente MIPS MT que añade funcionalidades multithreading similares a la tecnología HyperThreading de los procesadores Intel Pentium 4.

Debido a que los diseñadores crearon un conjunto de instrucciones tan claro, los cursos sobre arquitectura de computadores en universidades y escuelas técnicas a menudo se basan en la arquitectura MIPS. El diseño de la familia de CPU's MIPS influiría de manera importante en otras arquitecturas RISC posteriores como los DEC Alpha.

El uso del MIPS como procesador principal de estaciones de trabajo ha caído, y SGI ha anunciado sus planes de cesar el desarrollo de iteraciones de alto rendimiento de la arquitectura MIPS en favor de procesadores basados en la tecnología Intel IA64 (véase la sección "Otros modelos y planes futuros").

Por otra parte, el uso de microprocesadores MIPS en sistemas embebidos es probable que se mantenga gracias al bajo consumo de energía y características térmicas de las implementaciones integradas, así como a la gran disponibilidad de herramientas de desarrollo y de expertos conocedores de la arquitectura.

En los últimos años gran parte de la tecnología empleada en las distintas generaciones MIPS ha sido ofrecida como diseños de "IP-cores" (bloques de construcción) para sistemas embebidos. Se ofertan los núcleos básicos de 32 y 64 bits, conocidos respectivamente como 4K y 5K respectivamente, y con licencias MIPS32 y MIPS64. Estos núcleos pueden ser combinados con unidades añadidas tales como FPUs, sistemas SIMD, dispositivos de E/S, etc.

Los núcleos MIPS han sido comercialmente exitosos, siendo empleados actualmente en muchas aplicaciones industriales y de consumo. Pueden encontrarse en los más modernos routers Cisco y Linksys , cablemódems y módems ADSL, tarjetas inteligentes, controladoras de impresoras láser, decodificadores de TV, robots, ordenadores de mano, Sony PlayStation 2 y Sony PlayStation Portable.

En móviles y PDA's, sin embargo, el núcleo MIPS fue incapaz de desbancar a su competidor de arquitectura ARM.

Tendencia de preferencia de procesadores embebidos

Encuesta realizada en el año 2007 por el sitio Linux for devices

Referencias:

http://es.wikipedia.org/wiki/ARM

http://es.wikipedia.org/wiki/MIPS_%28procesador%29

http://mips.com/products/cores/